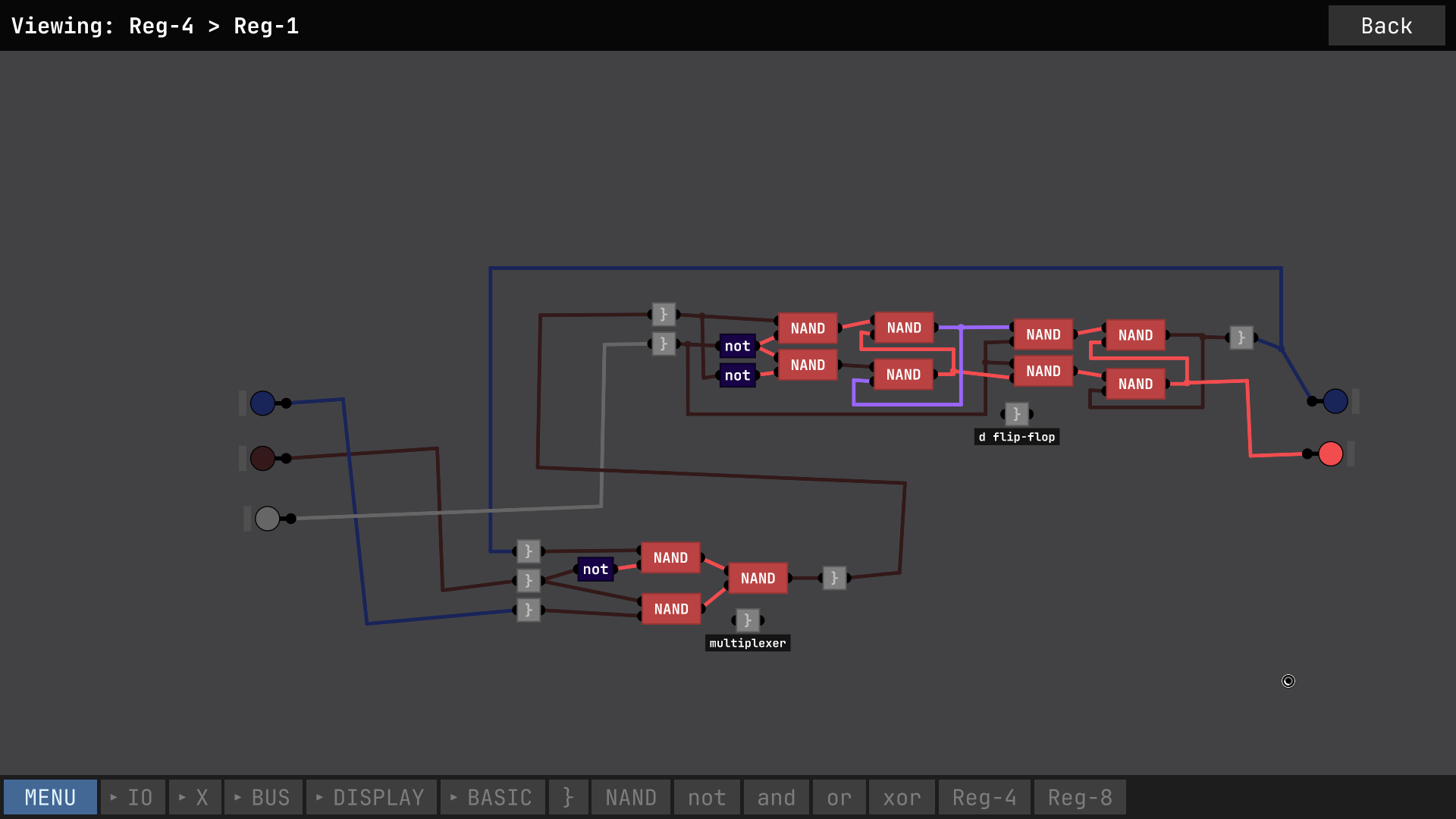

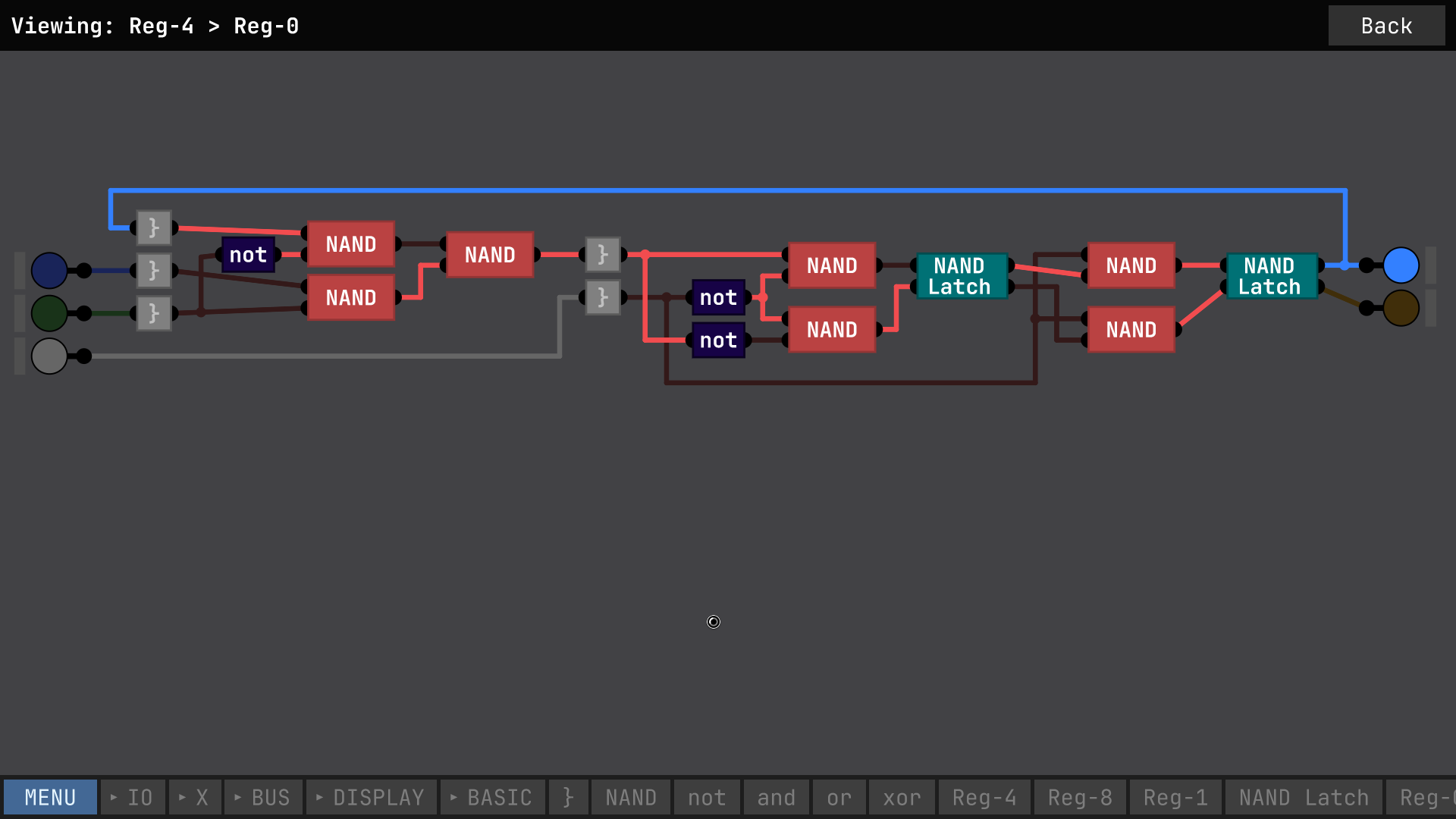

Please excuse my sloppy wiring. I have highlighted in Violet here the offending signal, which flickers in only some instances of this chip.

I don't really understand why this flickering signal is happening. My understanding is that the NAND SR latch should only have a race condition if both the inputs are *high*. Is there some obvious thing I'm doing wrong or some way to fix this? Note that the gray bracket chips just pass the data through, they're just an easy way to re-connect multiple things at once.