Correct

EDIT:

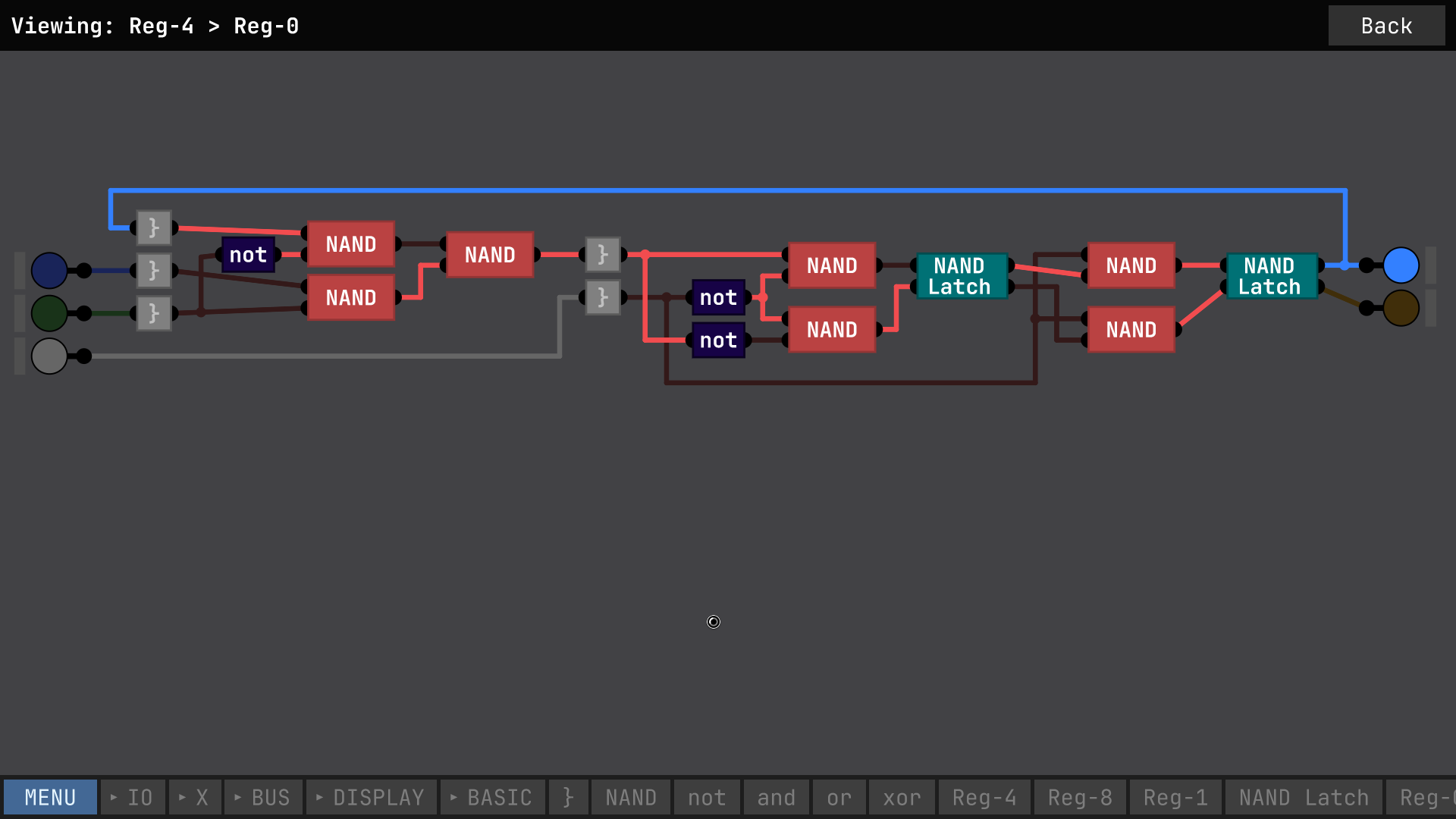

Just so you know there is some known funkiness in the simulation with latches both SR-style and RS-style (or any feedback loop, really) and how their initial starting conditions (which are random) affect their future timing behavior. Sometimes it can take an extra tick to set, sometimes an extra tick to reset. Once the initial state is determined, it will be consistent, but there's no way to determine how it will act before the initial state settles.

Also (and there's some nuance to this that I'm going to skip over) RS latches that exist as their own component will always start Low, but an SR latch's will always start in an unknown state.

also if you use an RS-style latch, and have a NOT gate attached to the output to serve as the Q-compliment, there is a chance that you will have both the Q and the Q-compliment have the same value for one tick.