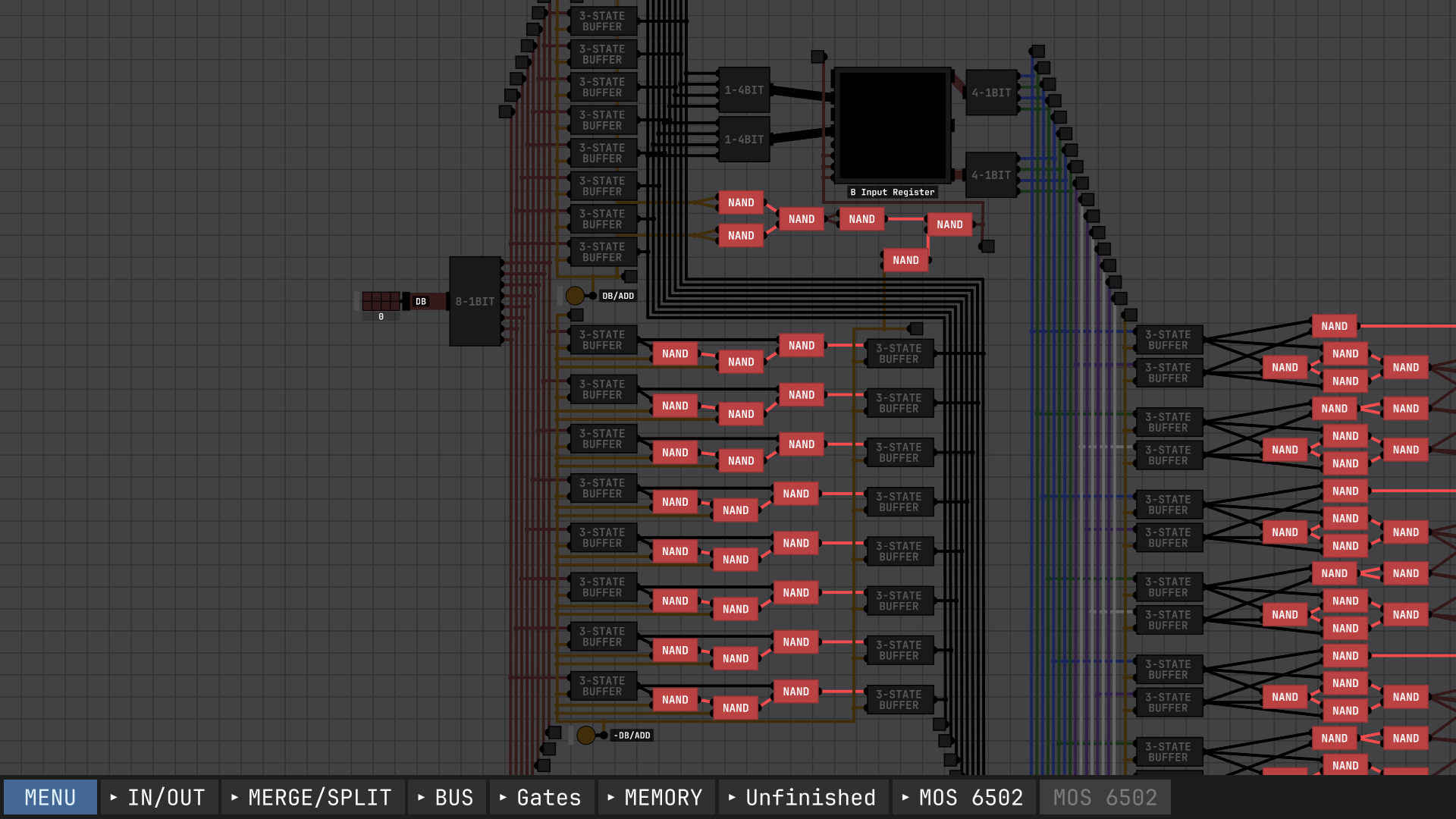

I started following along with Sebastian's videos but then I got carried away and made a working CPU based on Simple As Possible (SAP) CPU architecture.

I got it to work. in the video, it is doing Fibonacci series(up to 255 then things go weird for obvious reasons, I do have the key R bound to reset the CPU which I press a few times in the video if you wondered)

Some details about the architecture:

It only supports the following few instructions :

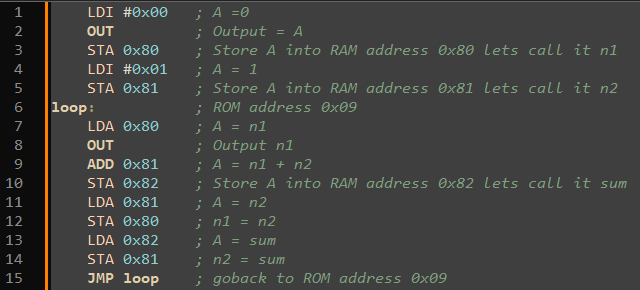

- NOP = (1 byte) No operation - OpCode = 0x00

- LDA = (2 bytes) Load Reg A (form Memory Address) - OpCode = 0x01

- ADD = (2 bytes) Add Value of memory address to A and stores it in A - OpCode = 0x02

- SUB = (2 bytes) Subtracts Value of memory address to A and stores it in A - OpCode = 0x03

- STA = (2 bytes) Stores Reg A into Memory Address - OpCode = 0x04

- LDI = (2 bytes) Load Reg A immediate value - OpCode = 0x05

- JMP = (2 bytes) JMP to address - OpCode = 0x06

- JC = (2 bytes) Jump if Carry to address - OpCode = 0x07

- JZ = (2 bytes) Jump if Zero (flag) to address - OpCode = 0x08

- OUT = (1 byte) loads whatever in A into the output register (therefore display) - OpCode = 0x0E

- HLT = (1 byte) Halts the program - OpCode = 0x0F

Addressing space is split only between RAM and ROM as follows:

- ROM address space is 0x00 to 0x7F (128bytes)

- RAM address space is 0x80 to 0xFF (128bytes)

the program it's running in the video can be represented as the screenshot below, which is stored in ROM as hex values directly, of course.

Here is the save file if you want it https://drive.google.com/file/d/1R2pp46HE2XlyOyXfhV24VUoxapS8Anuj/view

It should work on version 2.14. you can extract the save file here: %localappdata%\..\LocalLow\SebastianLague\Digital-Logic-Sim\Projects (if you are on windows)

Disclaimers:

- download and use at your own risk.

- It is not the most stable thing. could be a bug from the simulator itself or something off with the design. but it does take a few reloading the save file to get it to run smoothly and in a stable way.

- the save file includes some saved chips that are not used in this. SAP is the one that has the working implementation.

Key binds:

- R = Resets the counters

- S = Synchronizes (rests) all display settings. useful when using multiple display modules in the same chip and you want them to all have the same settings.

- T = Toggle between signed and unsigned 7seg displays

- B = turn on/off blanking on the 7seg displays