Bendy509

36

Posts

4

Topics

1

Following

A member registered Apr 21, 2025

Recent community posts

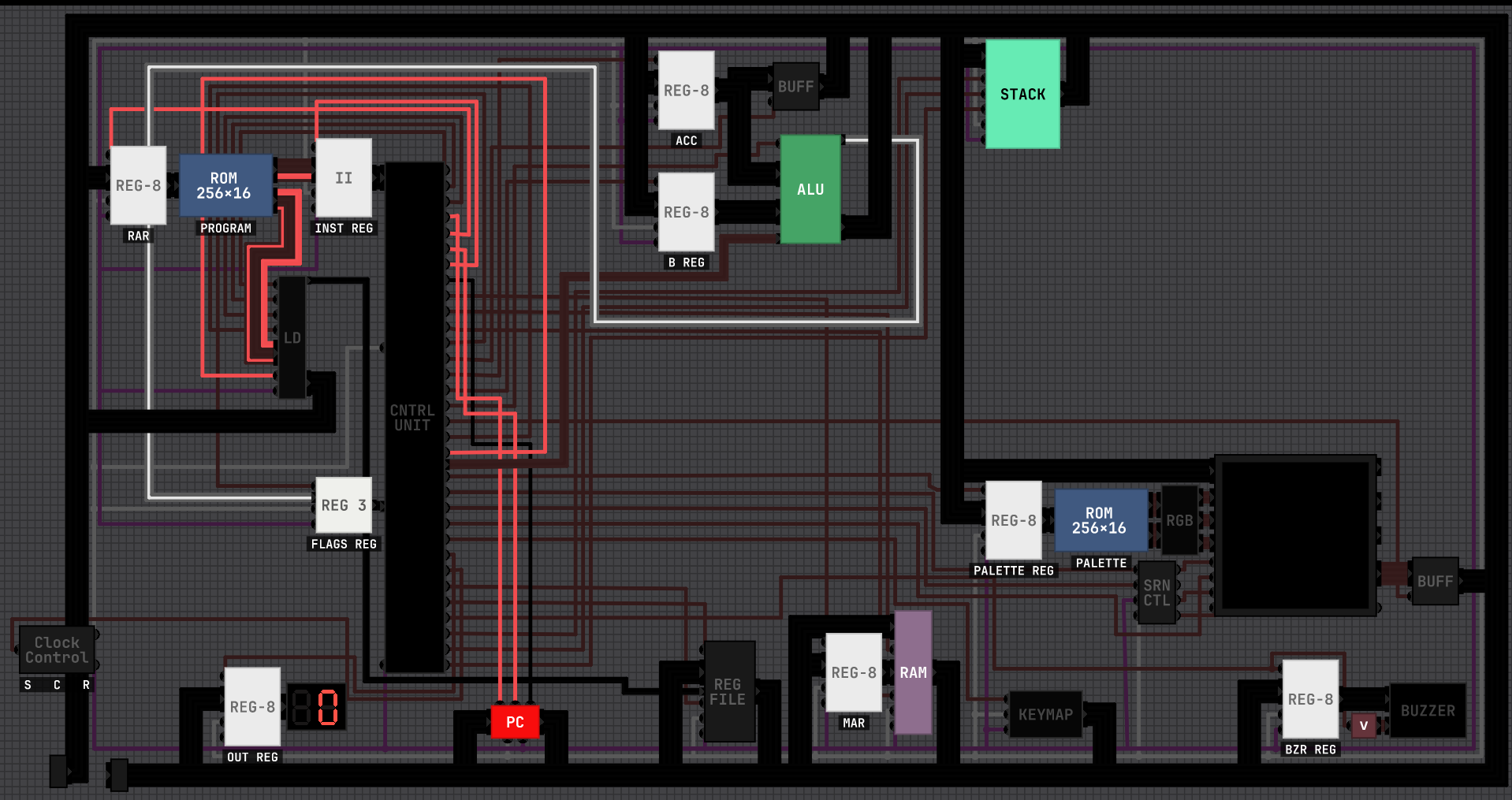

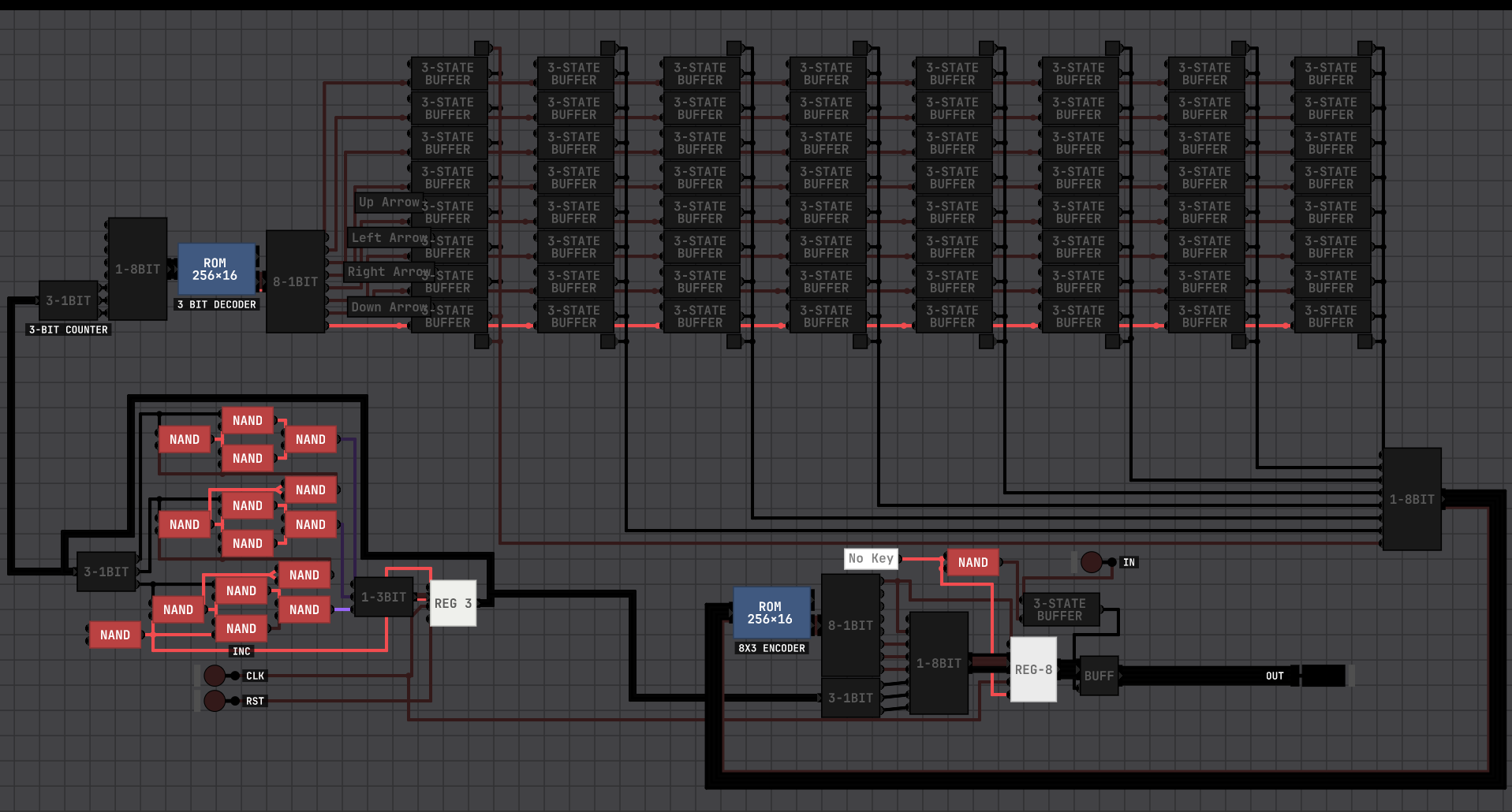

The more components you use, the slower the simulation became. You need to find the perfect steps per clock tick for your project. More component= More steps per clock tick.

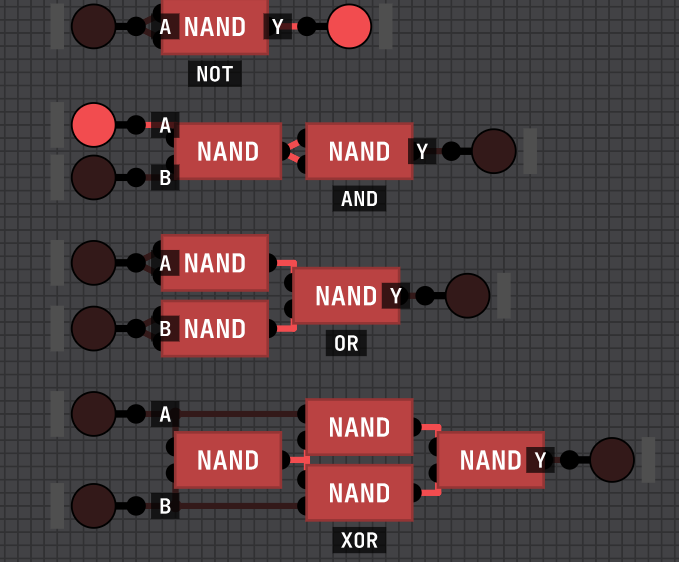

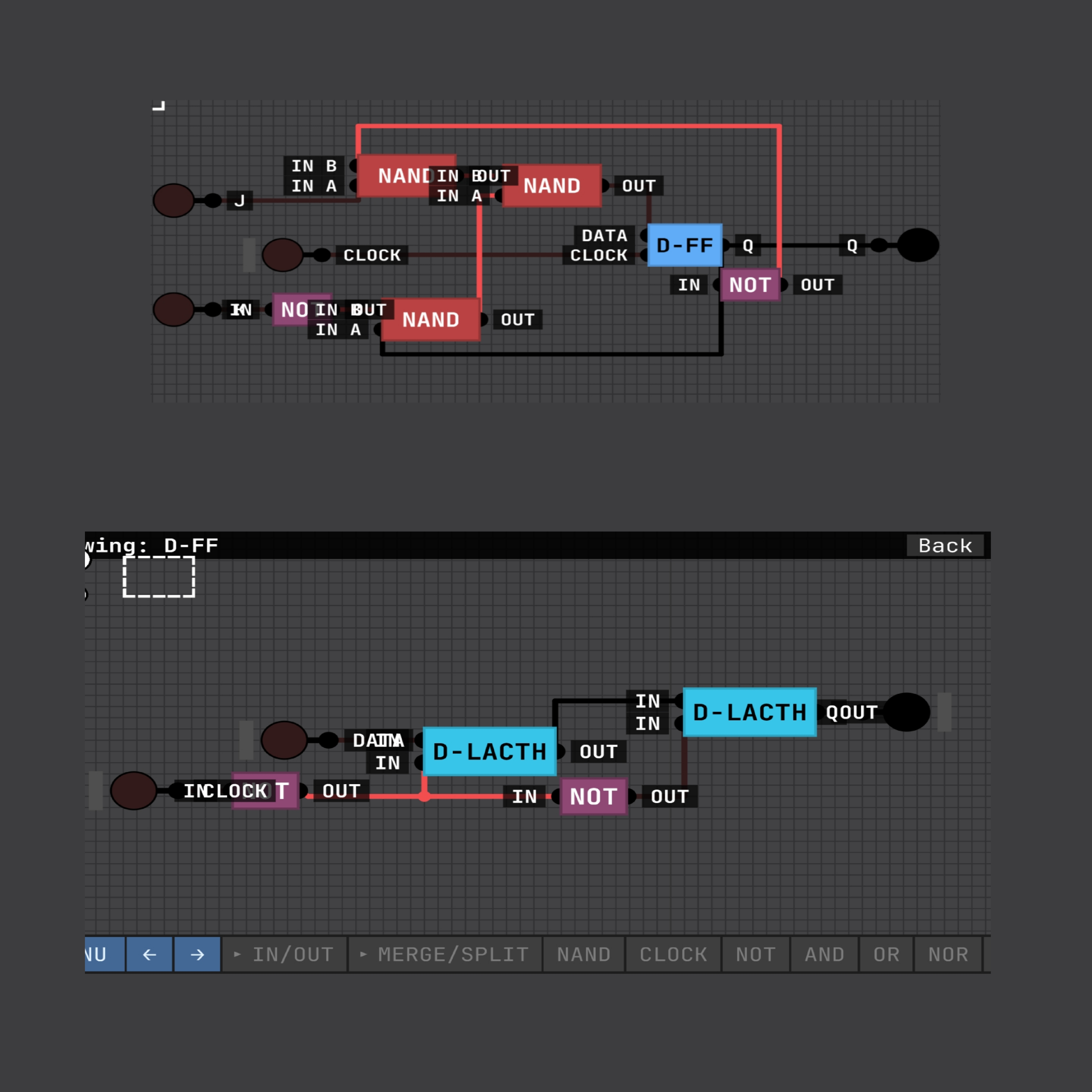

You can try to simplify by using less component. Create your chip via nand. Use ROM for decoder, 7 seg disp, etc... That's an 8-bits reg faster than the old ways.

That's an 8-bits reg faster than the old ways.

S= START/STOP

X=ONE STEP

C= CLEAR

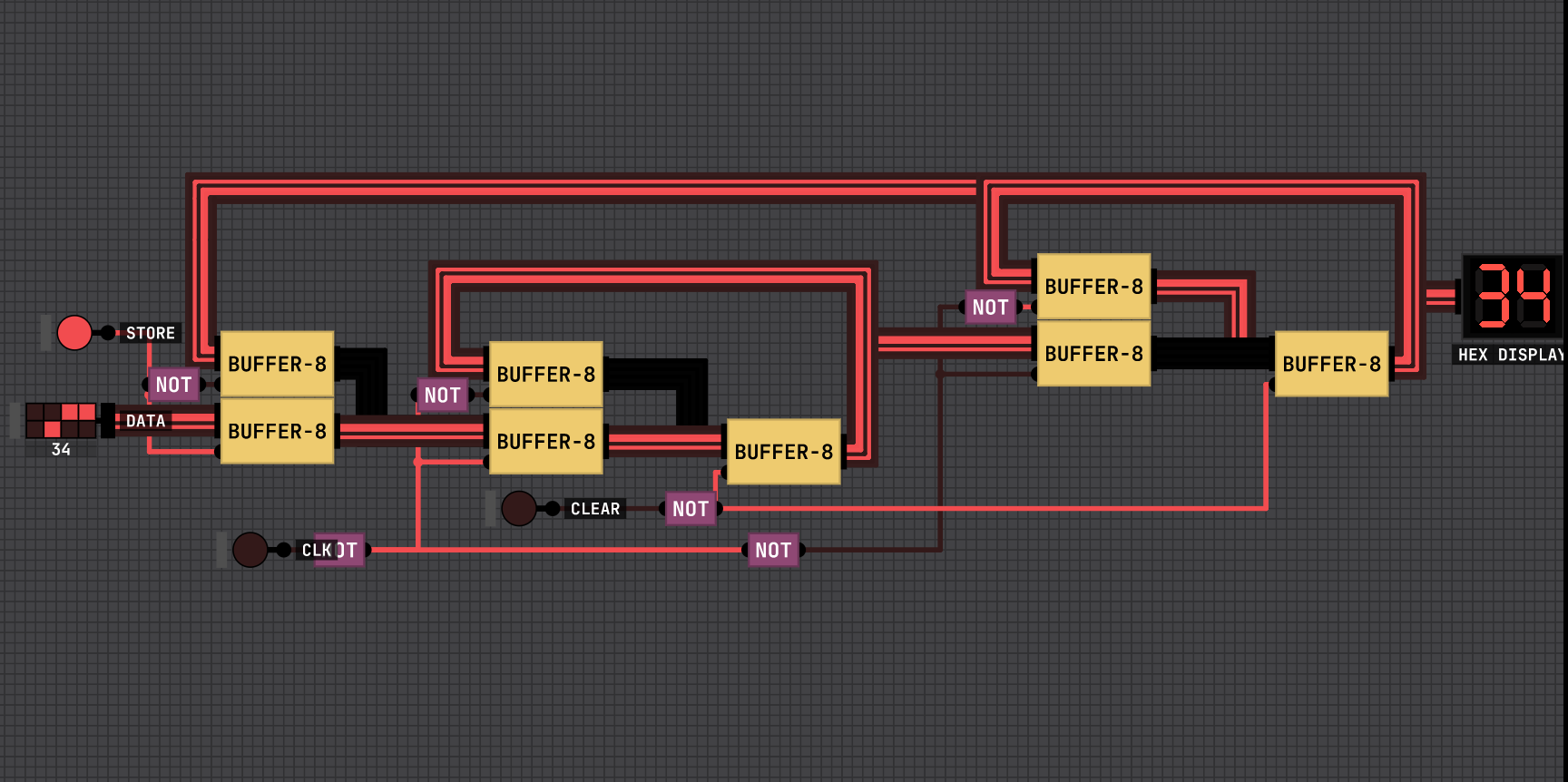

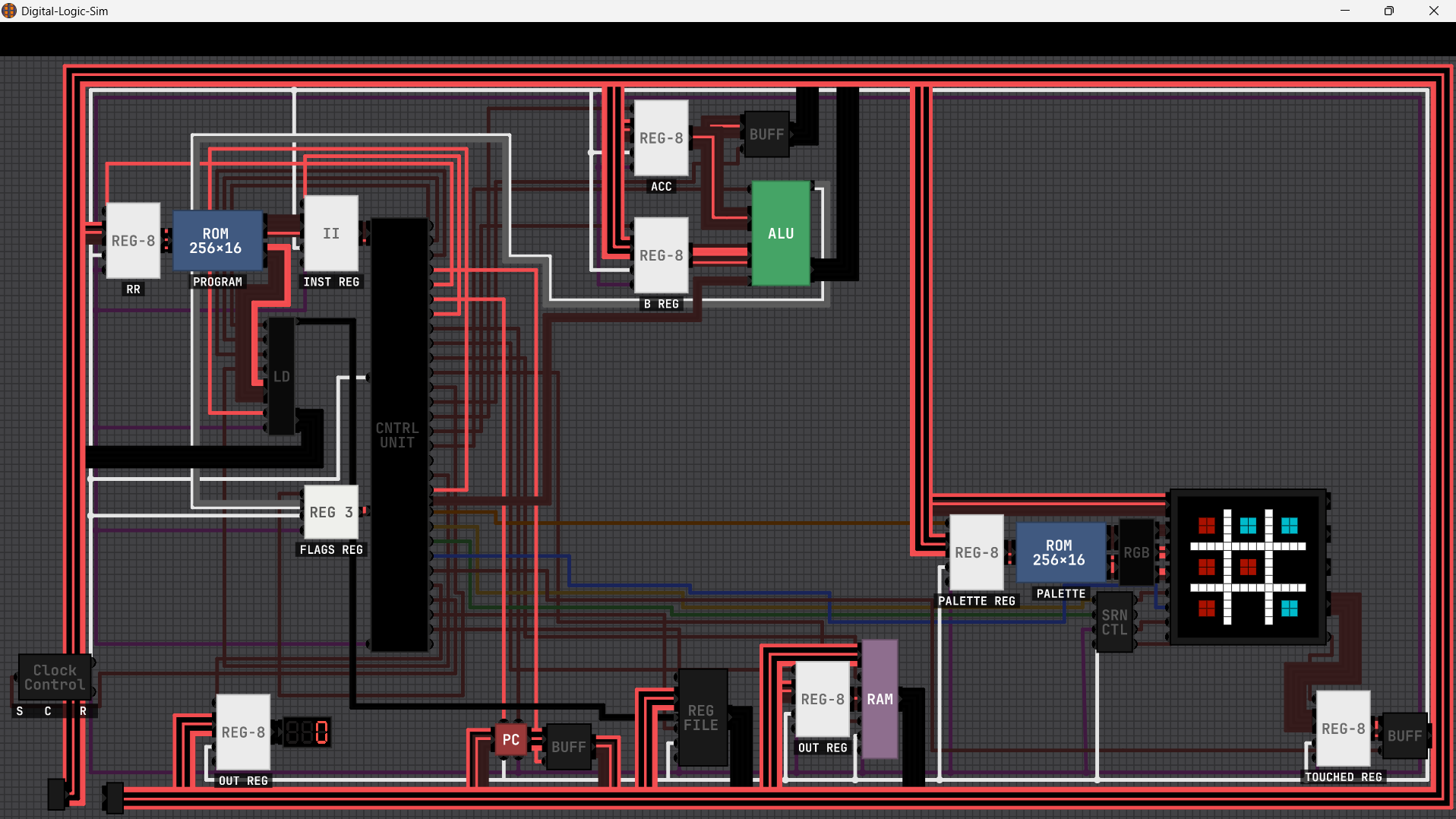

The visualization is in HEX code. The steps per clock stick must be at least 7.

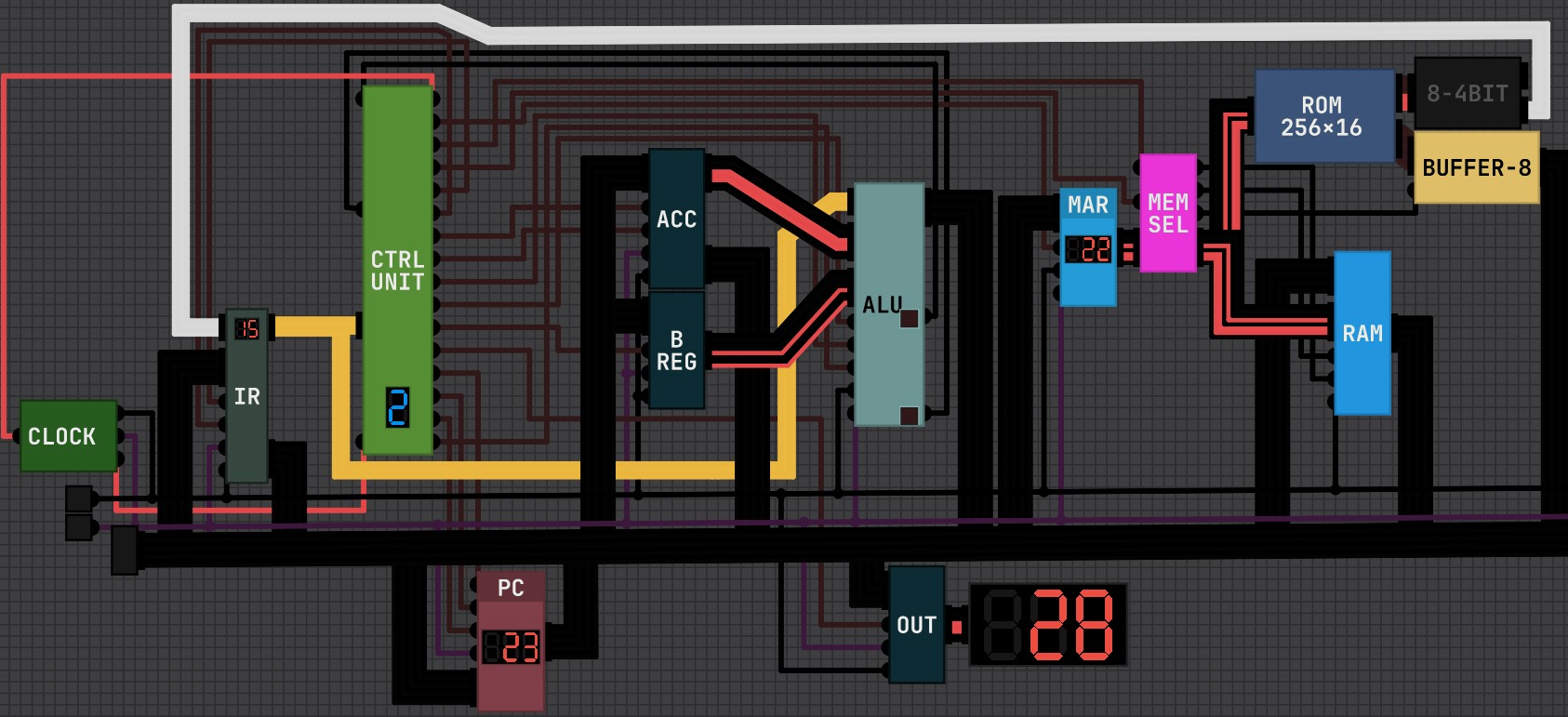

It has a multiplication (it also runs division) program on it (Multiplicand=0x000, Multiplier=0x002).

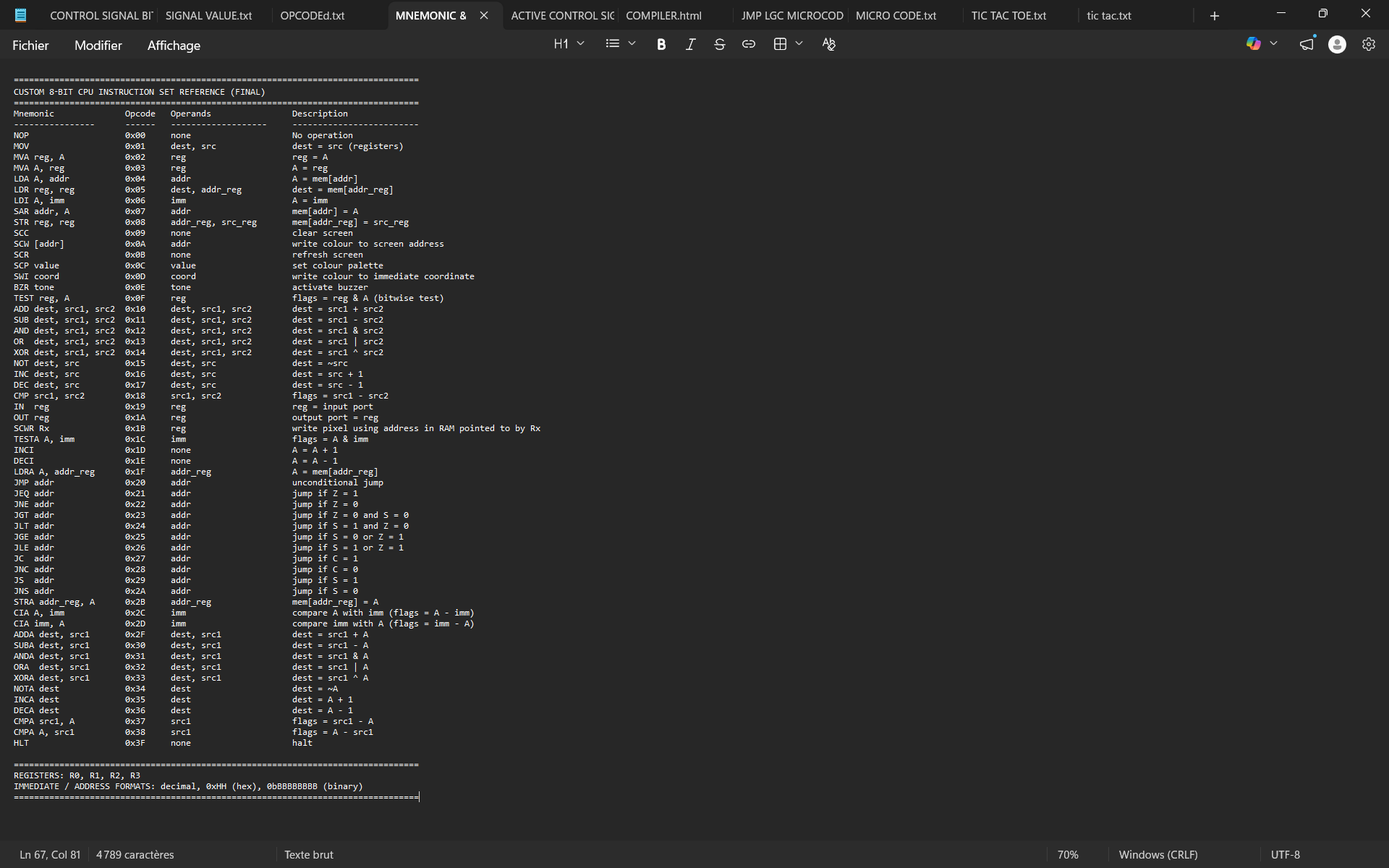

It's better when using HEX format to edit the ROM.

EX: LDX 5= 505 (Three digits. The 1st one is the instruction, and the rest is the data.

https://drive.google.com/file/d/1gX9fHKHZM2ACvy0F13JdNZ6kAkDKj9bM/view?usp=shari...

| INST | Bin | Function |

| NOP | 0000 | No operation |

| LDA | 0001 | Load accumulator from memory |

| ADD | 0010 | Add memory to accumulator |

| SUB | 0011 | Subtract memory from accumulator |

| STA | 0100 | Store accumulator to memory |

| LDX | 0101 | Load external register |

| JMP | 0110 | Jump to specified address |

| JC | 0111 | Jump if Carry is set |

| JZ | 1000 | Jump if accumulator is zero |

| JNC | 1001 | Jump if Carry is not set |

| JNZ | 1010 | Jump if accumulator is not zero |

| SHL | 1011 | Shift accumulator left |

| SHR | 1100 | Shift accumulator right |

| AND | 1101 | Bitwise AND with memory |

| OUT | 1110 | Output accumulator contents |

| HLT | 1111 | Halt execution |

Digital Logic Sim community · Replied to an gamer. (xcxx) or (the anthoian gamer) in what is the most effecient memory design

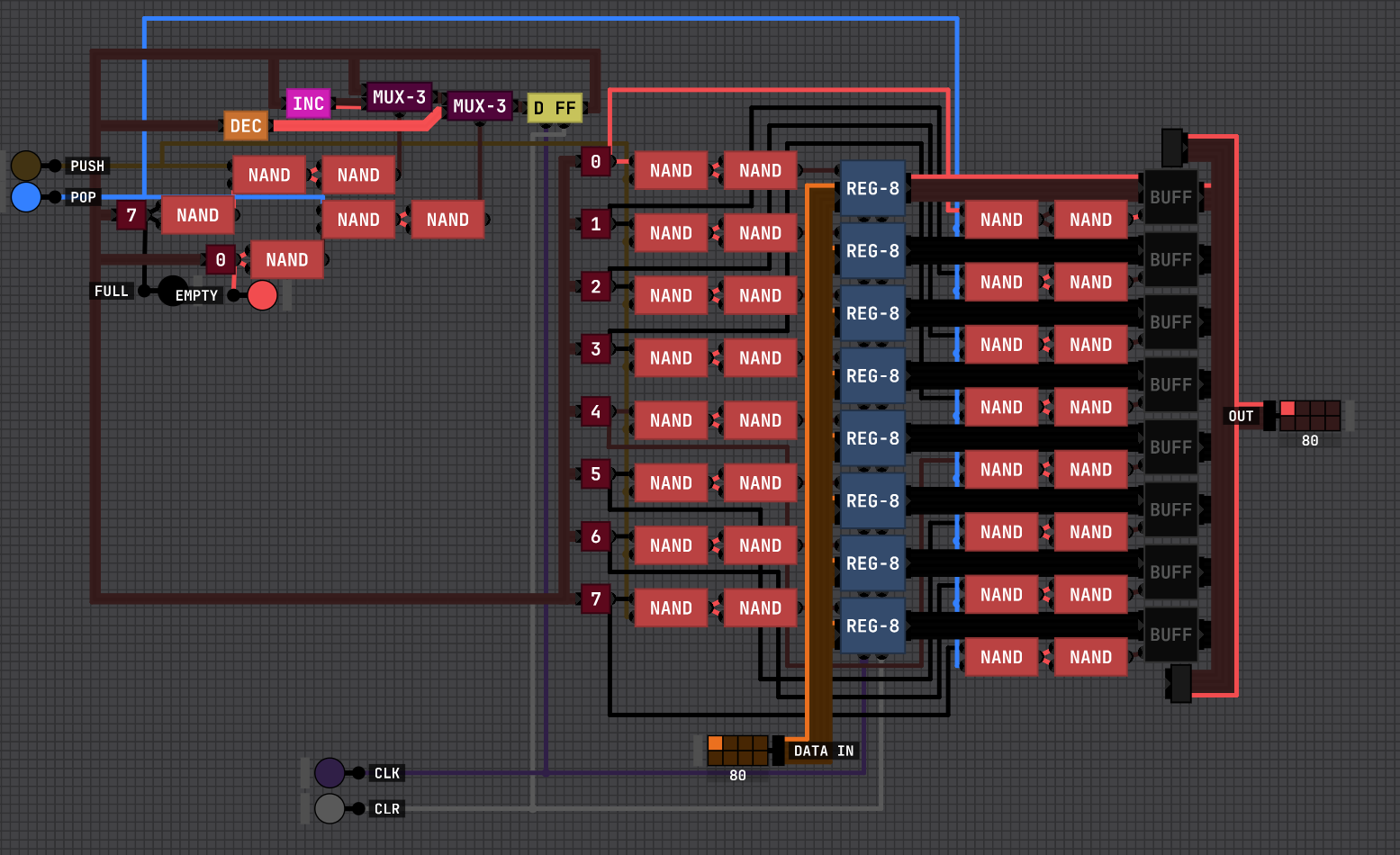

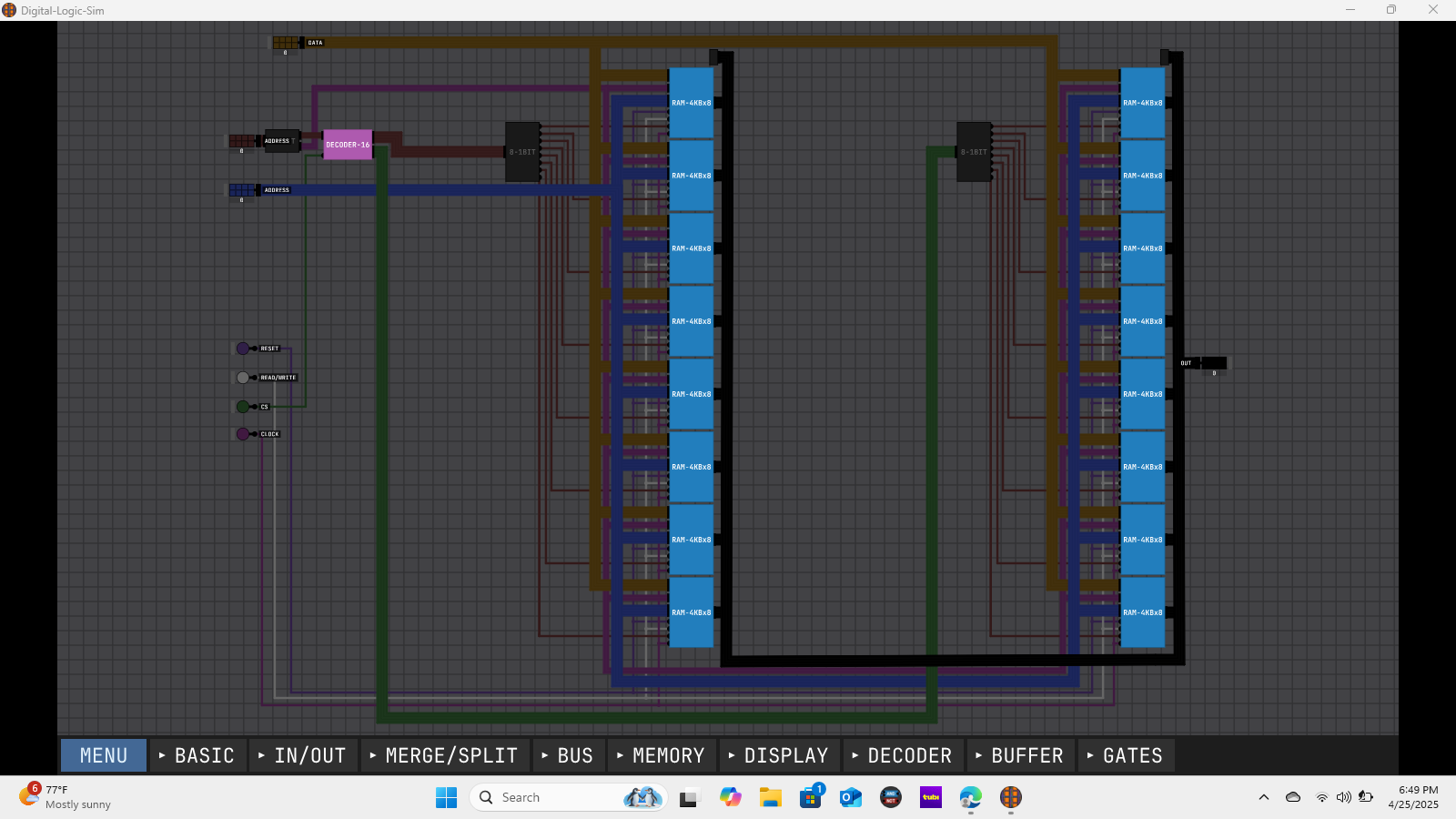

Here's the new version of my 64KB RAM (8 data lines I/O width.

I'm all ears for any suggestion. The link file also includes a 256B & 4KB RAM.

https://drive.google.com/file/d/1Q2a-aOKt2muEutrpK58V-gP_3YwMc2Mr/view?usp=shari...

I used RGB display. ...

I'm trying to build a large RAM capacity but the simulation gets slower every time I enhance it.

I'm stocked in 64KB because I need to pause the simulation for viewing or opening it.

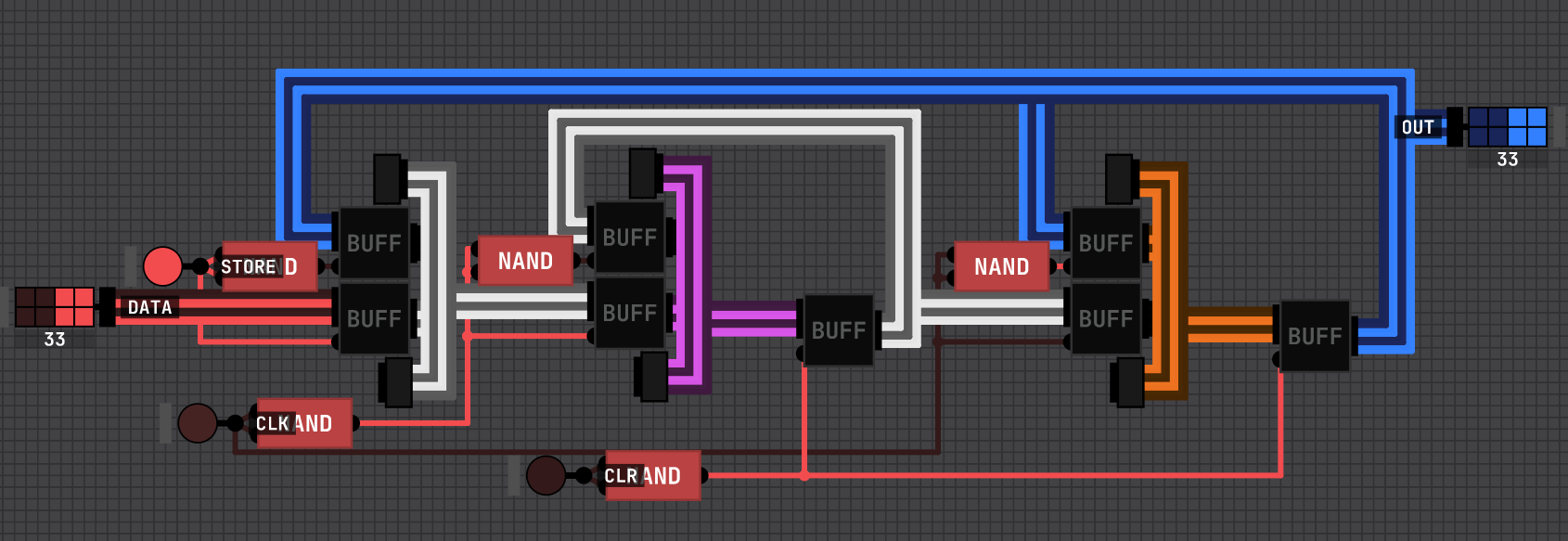

N.B: I use logic gates. the binary cell has 3 inputs {select, data, read/write}

Here is the file link: https://drive.google.com/file/d/1-1ifys702uznO3xJjQy0-F_d9KnuA7W_/view?usp=drive...

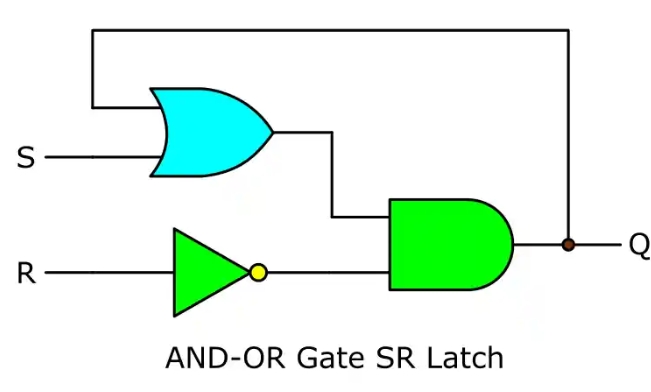

Hi guys,

I have constructed an SR latch, with its inputs (Set and Reset) connected to control signals and outputs as Q and Q̅. However, I am observing that upon using the chip, the latch does not initialize to a predictable state. Sometimes Q is high, and other times it is low, even though the inputs remain stable and no "illegal state" (S and R both high) is introduced.

Any advice or guidance you could provide would be greatly appreciated. Please let me know if you need further details or screenshots of the circuit design.

Thank you for your time and support.

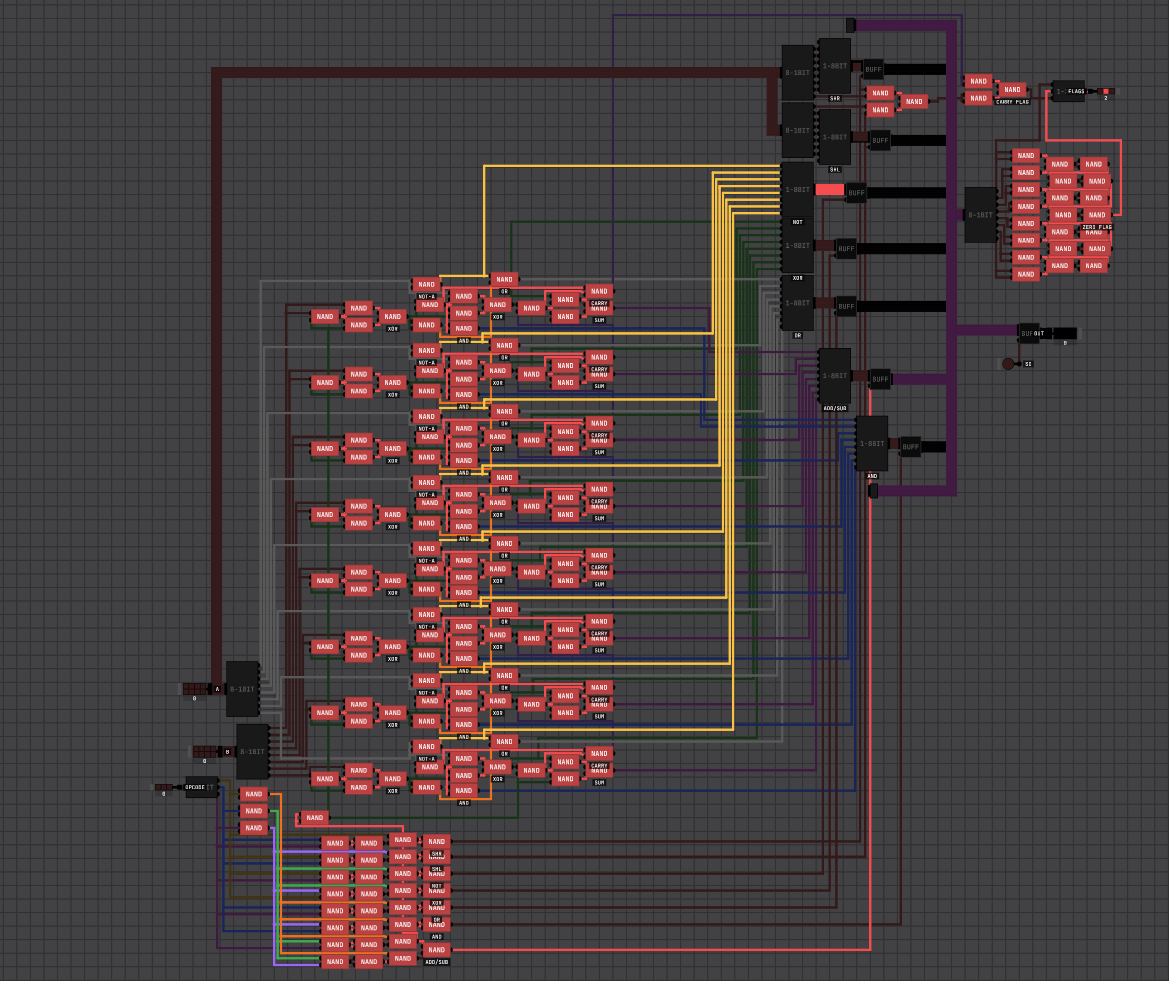

That's a 3-bit op ALU(add/sub, bitwise operation and shift) and three flags.

That's a 3-bit op ALU(add/sub, bitwise operation and shift) and three flags.