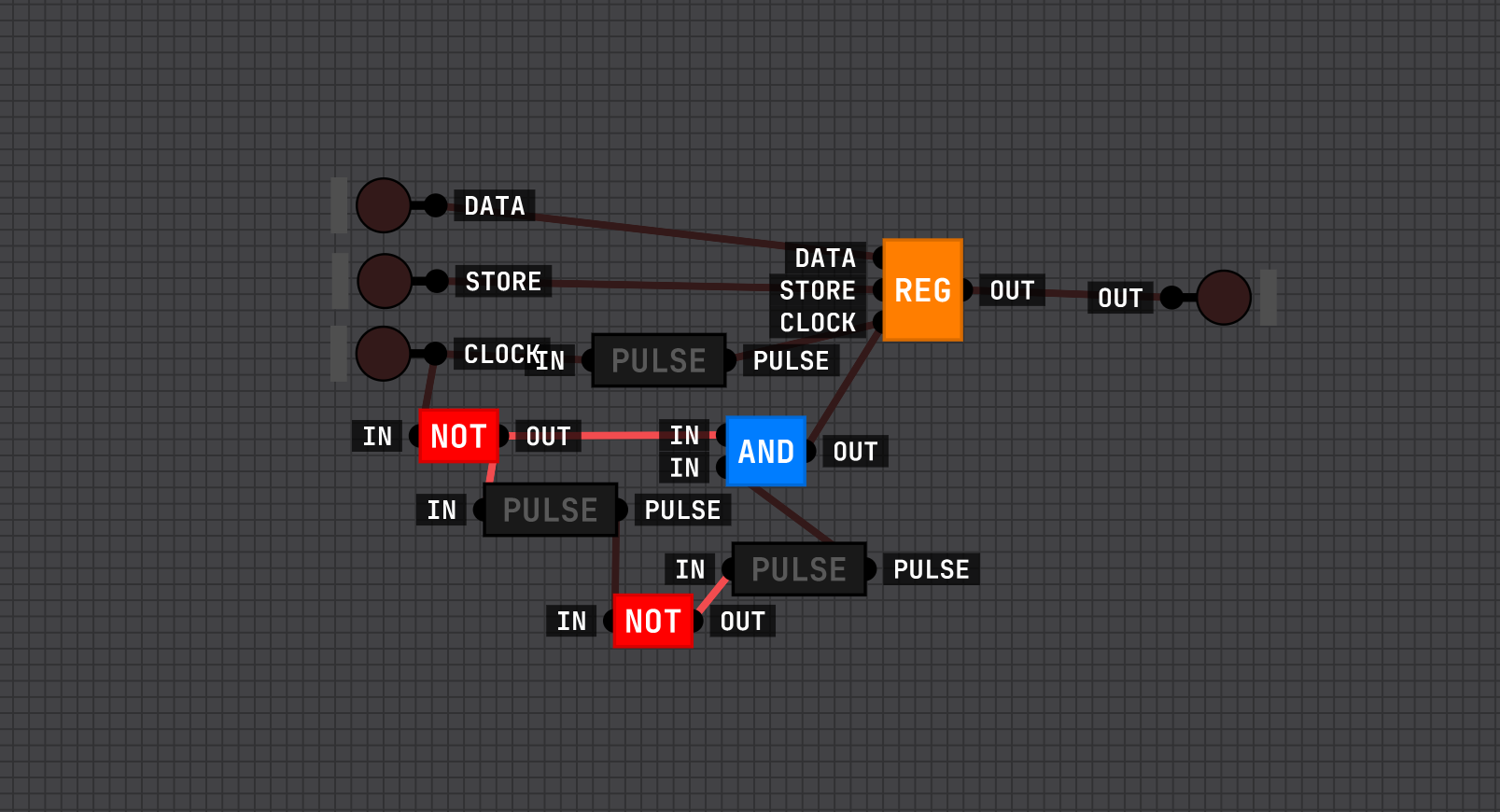

By using a delayed NOT pulse, I managed to make a DDR (Double Data Rate) register.

The only change from the outside compared to the regular register is that it also saves on the falling edge of the clock. It uses a delayed NOT pulse (CLOCK => NOT => PULSE => NOT => PULSE => AND with CLOCK => NOT => AND with AND => REG-CLOCK). The DATA and STORE signals were not changed, but a PULSE was added to the regular CLOCK signal because without it, enabling both STORE and CLOCK would just cause the output to be synced with DATA.

This is a big leap for me, so now I can put DDR registers into my custom CPU, which I'm still figuring out the ALU (multiply and divide part) for.

What do you think?

PHOTO: