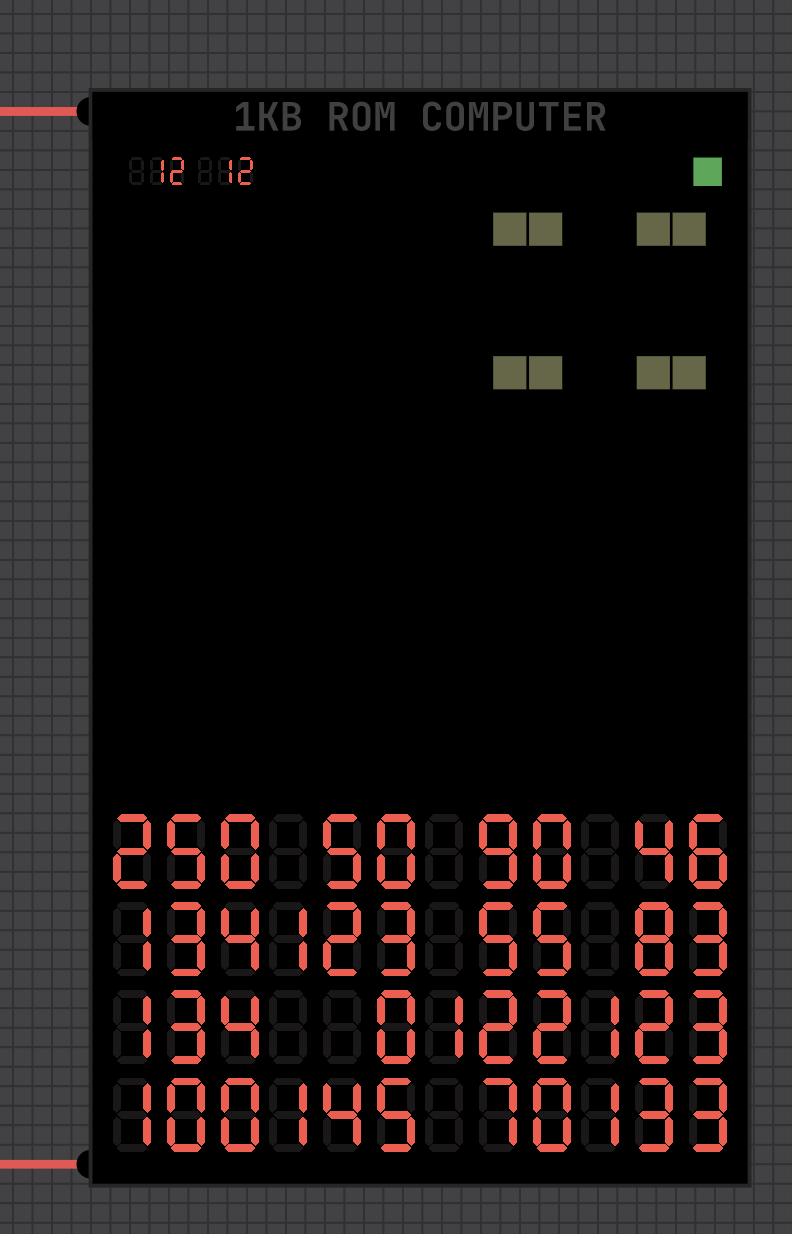

If you put a zero and one in to a bus it will be choose random of this inputs (Not the 3rd black state for zero). And with this you can make some random module. And for example if you have 2 zeros and 3 ones in to a bus, there will be %40 percent of 0 and %60 percent of 1. I think it's a very good feature but also there is a bug. The bug is when you put this randomness module some of them only give 0's or 1's in rising edge of clock. I think it's a bug but also maybe it's a good think because it brokes the simplest, smallest and most accurate randomness module. I want community's opinion of it. These are some patterns of 8-bit randomness modules:

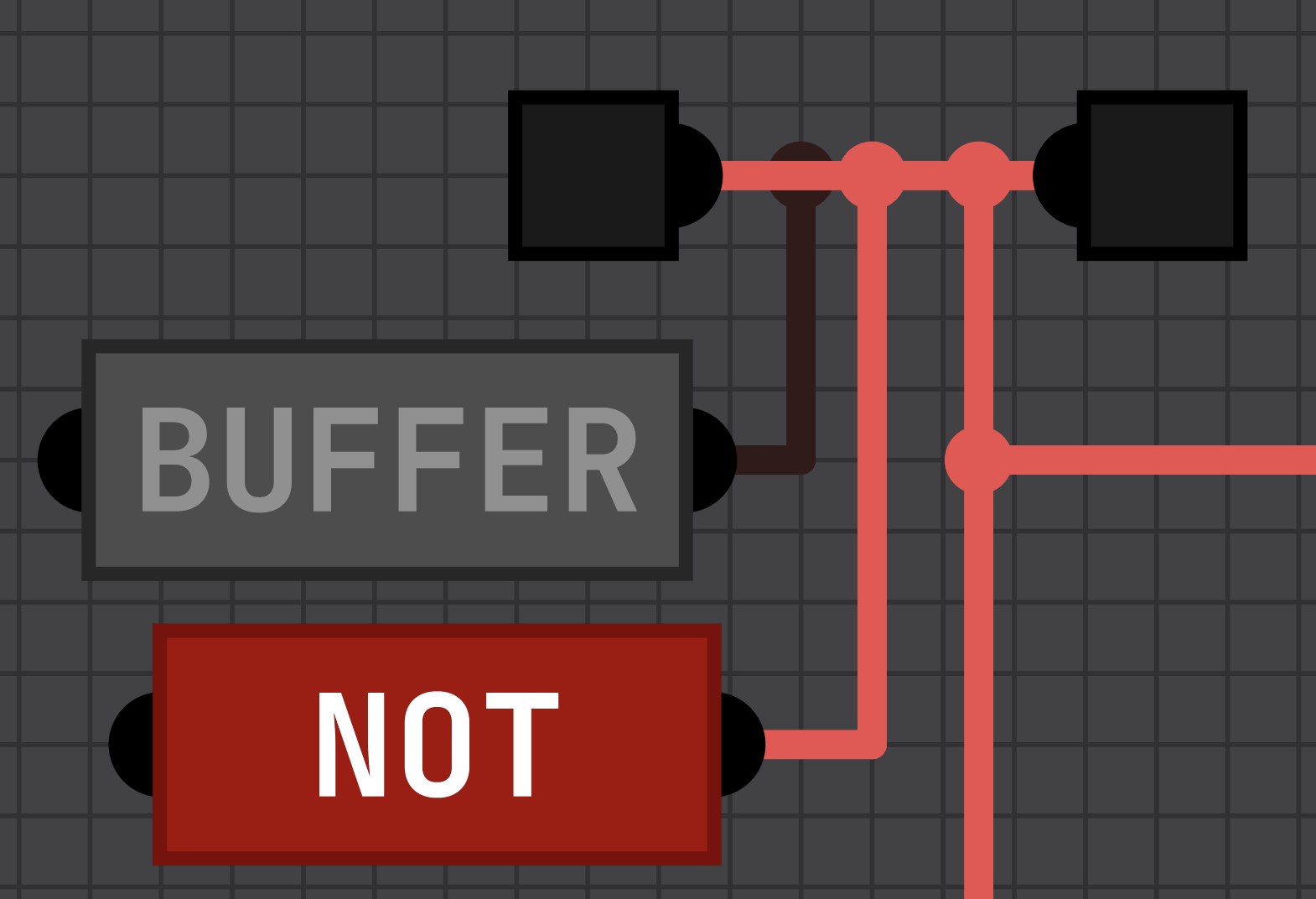

This is the inside of random module: